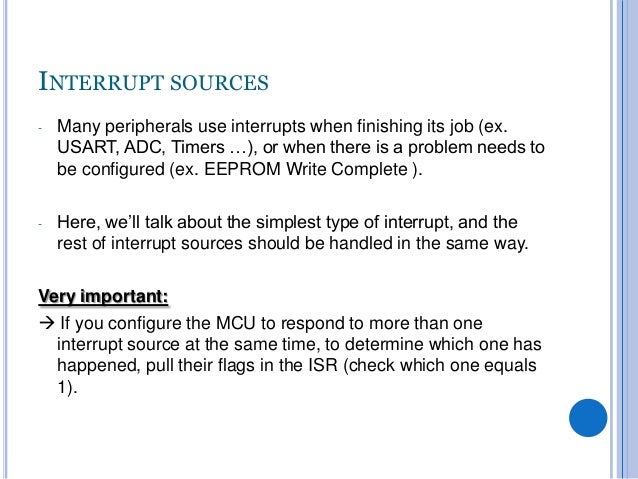

In doing so, the interrupt flag may be automatically cleared (depends on the design), the return address (address of the next instruction that was going to be executed) is saved, and perhaps some CPU flags are saved, and possibly some CPU registers are switched, and the ISR begins executing. If only one flag is found set, at the end of the current instruction the CPU jumps to, or "vectors to," that interrupt's ISR. If this is the case it means that there is no need for the ISR to explicitly clear the flag, as it will already be cleared by the time the ISR starts to run, but check the datasheet for any particular interrupt source to see if this is the case.Īny interrupt request flag that has been set, if the associated interrupt enable is set, is said to be "pending." If the microcontroller global interrupts are enabled, and one or more separate interrupts are enabled, the CPU hardware will automatically check all of these separate interrupt flags during the execution of every instruction. Second, the flag may be cleared automatically when the interrupt is responded to and the ISR begins to run. First, it can always be cleared manually by user code, usually by writing a '1' to the flag bit position in the associated register. The latched flag may be cleared in two different ways. It is this latched flag that actually generates the interrupt request. Most but not all interrupt requests are latched, which means the interrupt event sets a flag that stays set even if the interrupt event then goes away. Again this is in general terms, and different microcontroller designs may do things somewhat differently, but the basics remain the same. It's time to look a little closer at what happens in an interrupt request and response.

Part 1: Introduction to Microcontrollers - Beginnings.

0 kommentar(er)

0 kommentar(er)